Cadence Introduces C To Silicon Compiler Ee Times

Cadence Introduces C-to-Silicon Compiler - EE Times

Cadence Introduces C-to-Silicon Compiler - EE Times Cadence design systems, inc. introduced c to silicon compiler, a high level synthesis product supporting the creation and re use of system on chip ip. On july 14th, cadence introduced c to silicon compiler, a next generation high level synthesis product that improves designer productivity up to 10x in creating and re using system on chip ip.

Cadence Celebrates EE|Times' 50th! - EE Times

Cadence Celebrates EE|Times' 50th! - EE Times C to silicon compiler enhances designer productivity up to 10 times in creating and re using system on chip (soc) ip. this compiler is focused on asics and delivers the same output benefits to soc ip blocks designers targeting altera and xilinx fpgas. The innovative technology in c to silicon compiler helps bridge the gap between register transfer level (rtl) models — commonly used to verify, implement, and integrate socs — and system level models, usually written in c/c and systemc. Increasing designer productivity up to 10 times in ip creation and re use, cadence design systems (news alert), a provider of global electronic design innovation, has introduced cadence c to silicon compiler. Cadence design systems, inc. (cdns news), the leader in global electronic design innovation, today introduced cadence® c to silicon compiler, a high level synthesis product that improves designer productivity up to 10 times in creating and re using system on chip ip.

Silicon Carbide - EE Times

Silicon Carbide - EE Times Increasing designer productivity up to 10 times in ip creation and re use, cadence design systems (news alert), a provider of global electronic design innovation, has introduced cadence c to silicon compiler. Cadence design systems, inc. (cdns news), the leader in global electronic design innovation, today introduced cadence® c to silicon compiler, a high level synthesis product that improves designer productivity up to 10 times in creating and re using system on chip ip. The folks at cadence design systems have announced the integration of fpga synthesis for altera and xilinx fpgas with the cadence c to silicon compiler, which is their flagship electronic system level (esl) technology for hardware design and implementation. The cadence c to silicon compiler is available now in limited production. c to silicon compiler will be demonstrated during the da show/cdnlive! conference starting july 17. In the continuing effort to make high level synthesis more viable to mainstream rtl designers, cadence has released version 10.1 of the cadence c to silicon compiler (ctos). this new release continues the recent trend towards overall ease of use and quality of results. The latest release of the c to silicon compiler extends these capabilities from asics to fpgas, with the same benefits. "the c to silicon compiler very effectively handles mixed control/datapath designs, as well as incremental synthesis," said steve svoboda, product marketing director at cadence.

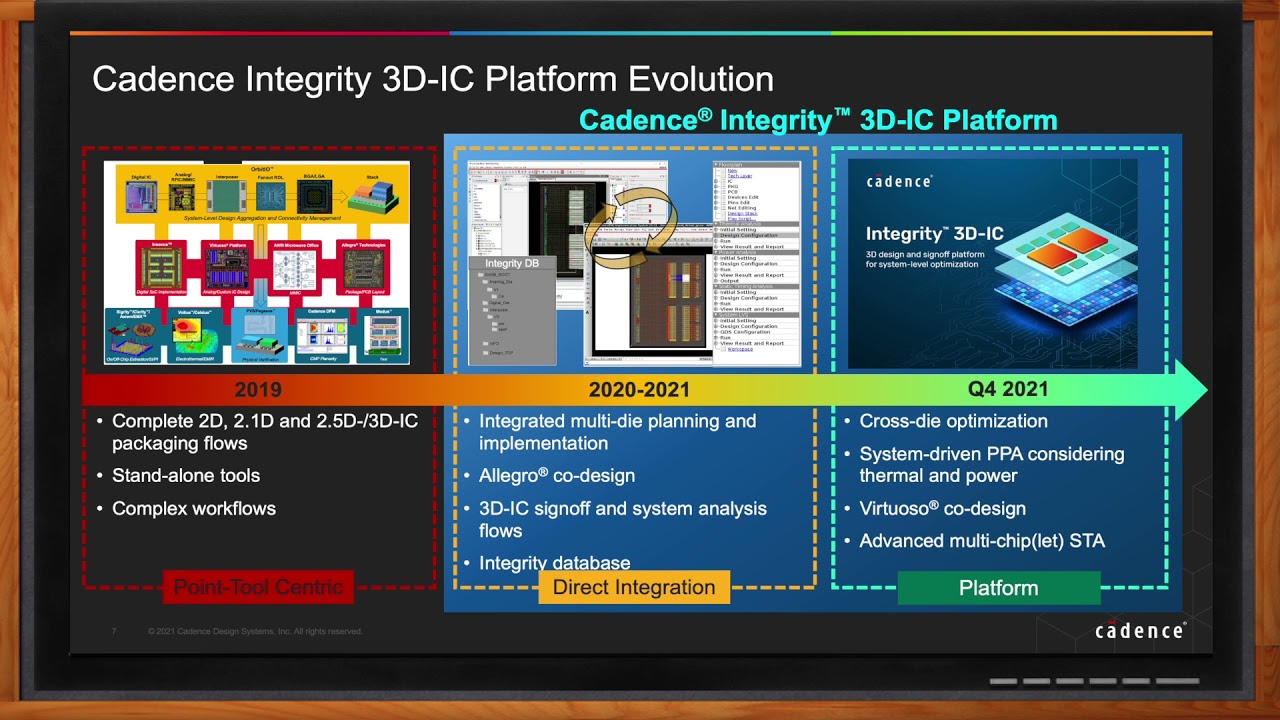

Faster, More Predictable Path to Multi-Chiplet Design Closure -- Cadence Design Systems

Faster, More Predictable Path to Multi-Chiplet Design Closure -- Cadence Design Systems

Related image with cadence introduces c to silicon compiler ee times

Related image with cadence introduces c to silicon compiler ee times

About "Cadence Introduces C To Silicon Compiler Ee Times"

Comments are closed.