Free Video Smashing The Implementation Records Of Aes S Box From Theiacr Class Central

Effective Aes Implementation | PDF | Cryptography | Key (Cryptography)

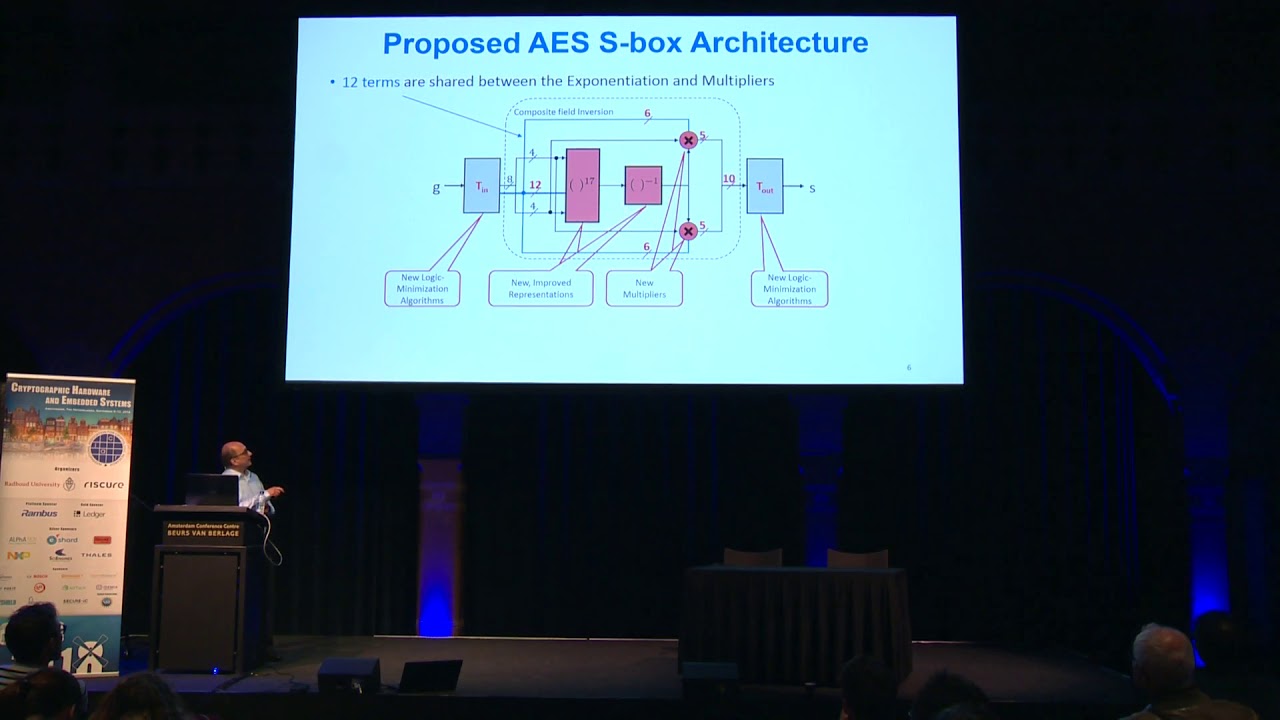

Effective Aes Implementation | PDF | Cryptography | Key (Cryptography) Paper by arash reyhani masoleh and mostafa m. i. taha and doaa ashmawy, presented at ches 2018. see https://www.iacr.org/cryptodb/data/paper ?pubkey=28960. Gain valuable insights into state of the art cryptographic engineering techniques and their practical applications in this 21 minute presentation from theiacr. explore innovative techniques for optimizing aes s box implementation, focusing on logic minimization, exponentiation, and output multipliers to achieve record breaking performance.

Free Video: Smashing The Implementation Records Of AES S-Box From TheIACR | Class Central

Free Video: Smashing The Implementation Records Of AES S-Box From TheIACR | Class Central In ches’15, ueno et al. proposed an s box that has a slightly higher area, but significantly faster than the previous designs, hence it was the most efficient (measured by area×delay) s box implementation to date. in this paper, we propose two new designs for the aes s box. Explore advanced cryptanalysis techniques and security assessments of the advanced encryption standard (aes) through expert led discussions from asiacrypt 2024. In ches’15, ueno et al. proposed an s box that has a slightly higher area, but significantly faster than the previous designs, hence it was the most efficient (measured by area×delay) s box implementation to date. in this paper, we propose two new designs for the aes s box. In ches’15, ueno et al. proposed an s box that has a slightly higher area, but significantly faster than the previous designs, hence it was the most efficient (measured by area×delay) s box.

Aes | PDF | Encryption | Programming

Aes | PDF | Encryption | Programming In ches’15, ueno et al. proposed an s box that has a slightly higher area, but significantly faster than the previous designs, hence it was the most efficient (measured by area×delay) s box implementation to date. in this paper, we propose two new designs for the aes s box. In ches’15, ueno et al. proposed an s box that has a slightly higher area, but significantly faster than the previous designs, hence it was the most efficient (measured by area×delay) s box. Explore aes encryption and isa extensions, covering fixed sliced encryption, scalar isa design, and aes lbb. learn about tag verification, generation, and sp evaluation. Bitslice masking and improved shuffling: how and when to mix them in software? sok: sca secure ecc in software – mission impossible? soc root canal! : root cause analysis of power side channel leakage in system on chip designs. Use only simple gates, when compound gates (and or invert, or and invert) may be more efficient. use and gates, when nand gates have smaller area and delay in all technology libraries. use only simple gates, when compound gates (and or invert, or and invert) may be more efficient. In ches’15, ueno et al. proposed an s box that has a slightly higher area, but significantly faster than the previous designs, hence it was the most efficient (measured by area×delay) s box.

Smashing the Implementation Records of AES S box

Smashing the Implementation Records of AES S box

Related image with free video smashing the implementation records of aes s box from theiacr class central

Related image with free video smashing the implementation records of aes s box from theiacr class central

About "Free Video Smashing The Implementation Records Of Aes S Box From Theiacr Class Central"

Comments are closed.