Live Fpga Adcs Part 4 Psram Framebuffer Beamforming

FPGA Adaptive Beamforming With HDL Coder And Zynq RFSoC | PDF | Hardware Description Language ...

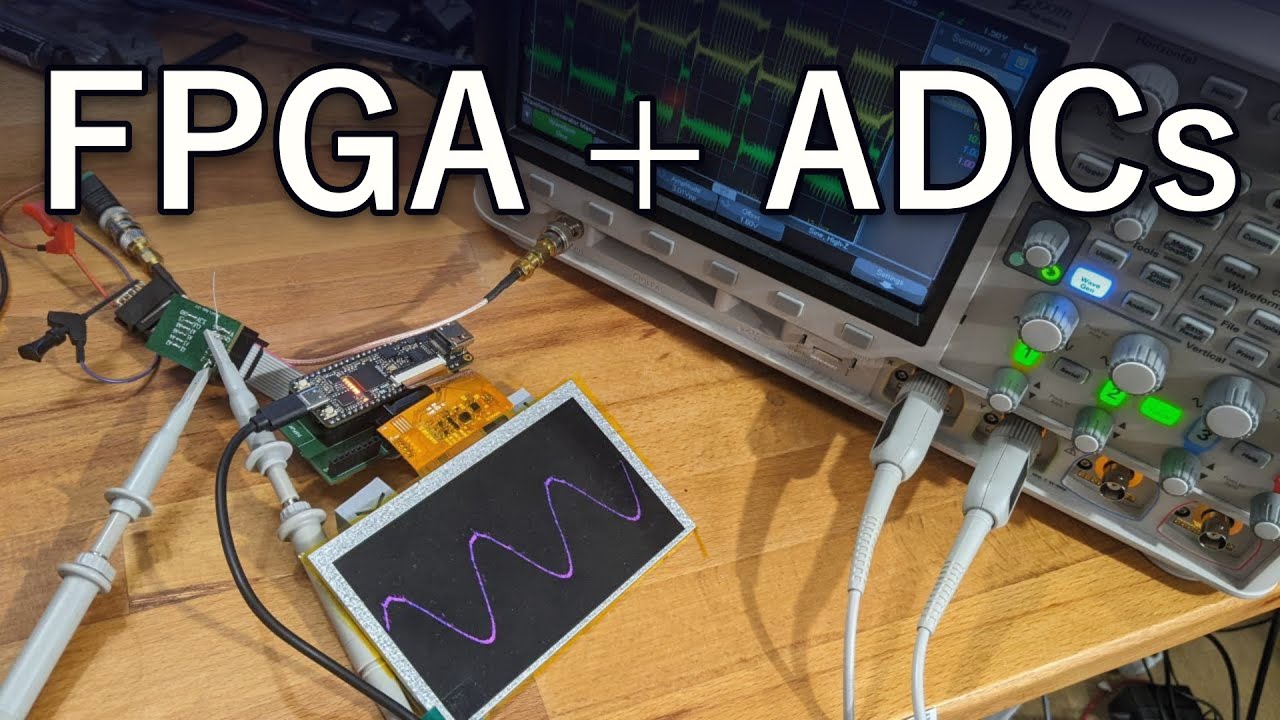

FPGA Adaptive Beamforming With HDL Coder And Zynq RFSoC | PDF | Hardware Description Language ... I found a way to access the psram of the fpgas. it's tricky but i think we can use it for a frame buffer and take our time to render a beamformed frame from the recorded adc samples. We further demonstrate a prototyping workflow by deploying the beamformer to the zcu111 rfsoc evaluation board for run time testing, debugging and visualization. this model uses the phased array toolbox to demonstrate high level modeling of adaptive beamforming processing.

Implementing And ADC Inside The FPGA | Controlpaths.com

Implementing And ADC Inside The FPGA | Controlpaths.com This project aims to detect the static and moving objects in the room and implement the imaging with the beamforming algorithm running on the avnet ® zedboard. since this is a logic design and verification course, maybe the best practice is to perform all the functionalities on the fpga fabric. Buf two frame buffer in internal sram is so big and i need to change the location to psram. so i changed the address of frame buffer and frame buffer0 to psram address. but the display is crashed. i can't get screens that i wanted. as i mentioned, no problem when i use psram as animation storage buffer. using psram as a frame buffer is impossible?. “hybrid beamforming system design for 5g massive mimo arrays using matlab, phased array system toolbox, and 5g toolbox helped us in evaluating various hardware options as well as their performance in realistic 5g scenarios.”. In this article, we’ll describe the devel opment of a flexible, optimized, adaptive beamforming engine that you can easily control through software. the dsp inten sive tasks run on the fpga, while the com mand and control run on an external processor.

Noise On ADC Output When Toggling FPGA Pins - Q&A - High-Speed ADCs - EngineerZone

Noise On ADC Output When Toggling FPGA Pins - Q&A - High-Speed ADCs - EngineerZone “hybrid beamforming system design for 5g massive mimo arrays using matlab, phased array system toolbox, and 5g toolbox helped us in evaluating various hardware options as well as their performance in realistic 5g scenarios.”. In this article, we’ll describe the devel opment of a flexible, optimized, adaptive beamforming engine that you can easily control through software. the dsp inten sive tasks run on the fpga, while the com mand and control run on an external processor. Live: fpga \u0026 adcs part 4: psram, framebuffer, beamforming live: fpga \u0026 adcs part 4: psram, framebuffer, beamforming 4 stunden, 33 minuten i found a way to access the psram of the fpgas. it's tricky but i think we can use it for a frame buffer and take our time to render a€. I’ve read somewhere (and confirmed by the rp2350 architecture) that the psram and external flash share the same qspi bus. depending on the software implementation, this can lead to slowdowns or even a crash. To validate the proposed design, a xilinx zuc1287 evaluation fpga is selected. the digital design clocking at 250 mhz with 40 phases is implemented in the fpga. the 2 level output from the 40 phases from 8 channels are serialized through mgts that are configured to 10 gsps. This example shows how to implement an fpga ready beamformer to match a corresponding behavioral model in simulink by using the phased array system toolbox™, dsp system toolbox™, and fixed point designer™ libraries.

LIVE: FPGA & ADCs Part 4: PSRAM, Framebuffer, Beamforming

LIVE: FPGA & ADCs Part 4: PSRAM, Framebuffer, Beamforming

Related image with live fpga adcs part 4 psram framebuffer beamforming

Related image with live fpga adcs part 4 psram framebuffer beamforming

About "Live Fpga Adcs Part 4 Psram Framebuffer Beamforming"

Comments are closed.