Low Power Design Techniques Span Rtl To Gdsii Flow Ee Times

Low-power Design Techniques Span RTL-to-GDSII Flow - EE Times

Low-power Design Techniques Span RTL-to-GDSII Flow - EE Times In order to enable designers to accurately and efficiently perform these tradeoffs, it is necessary for low power optimization techniques to be integrated with, and applied throughout, the entire rtl to gdsii flow. From a chip engineering perspective, effective energy management for an soc must be built into the design starting at the architecture stage; and low power techniques need to be employed at every stage of the design, from rtl to gdsii.

Low-power Design Techniques Span RTL-to-GDSII Flow - EE Times

Low-power Design Techniques Span RTL-to-GDSII Flow - EE Times This project presents the complete digital design flow of a low power system on chip (soc) that features multiple power and clock domains with advanced power gating and state retention. In this paper, we have reported low power cache memory with dft and scan chain techniques utilizing rtl to gds (register transfer level to graphic design system. Addressing the problems associated with dsm and udsm devices requires power design and analysis tools that work throughout the entire rtl to gdsii design flow. identifying and resolving power problems late in the flow results in expensive, time consuming iteration cycles. Creating optimal low power designs involves making tradeoffs such as timing versus power and area versus power at different stages of the design flow. successful power sensitive designs require engineers to have the ability to accurately and efficiently perform these tradeoffs.

Low-power Design Techniques Span RTL-to-GDSII Flow - EE Times

Low-power Design Techniques Span RTL-to-GDSII Flow - EE Times Addressing the problems associated with dsm and udsm devices requires power design and analysis tools that work throughout the entire rtl to gdsii design flow. identifying and resolving power problems late in the flow results in expensive, time consuming iteration cycles. Creating optimal low power designs involves making tradeoffs such as timing versus power and area versus power at different stages of the design flow. successful power sensitive designs require engineers to have the ability to accurately and efficiently perform these tradeoffs. Written in tcl, upf captures the low power design specification for use throughout the rtl to gdsii flow applying consistent semantics for both verification and implementation. In this guide, we’ll break down the rtl to gdsii process step by step, explain where outsourcing adds value, and how nsemi design ensures quality across the entire flow. Several techniques and methodologies have emerged to target low power design needs, however they do not contribute to reducing the operational or standby. Written in tcl, upf captures the low power design specification for use throughout the rtl to gdsii flow applying consistent semantics for both verification and implementation.

Tool Flow Depicting RTL To GDSII Flow | Download Scientific Diagram

Tool Flow Depicting RTL To GDSII Flow | Download Scientific Diagram Written in tcl, upf captures the low power design specification for use throughout the rtl to gdsii flow applying consistent semantics for both verification and implementation. In this guide, we’ll break down the rtl to gdsii process step by step, explain where outsourcing adds value, and how nsemi design ensures quality across the entire flow. Several techniques and methodologies have emerged to target low power design needs, however they do not contribute to reducing the operational or standby. Written in tcl, upf captures the low power design specification for use throughout the rtl to gdsii flow applying consistent semantics for both verification and implementation.

Total Power Optimization In RTL-to-GDSII Implementation Flow - EE Times

Total Power Optimization In RTL-to-GDSII Implementation Flow - EE Times Several techniques and methodologies have emerged to target low power design needs, however they do not contribute to reducing the operational or standby. Written in tcl, upf captures the low power design specification for use throughout the rtl to gdsii flow applying consistent semantics for both verification and implementation.

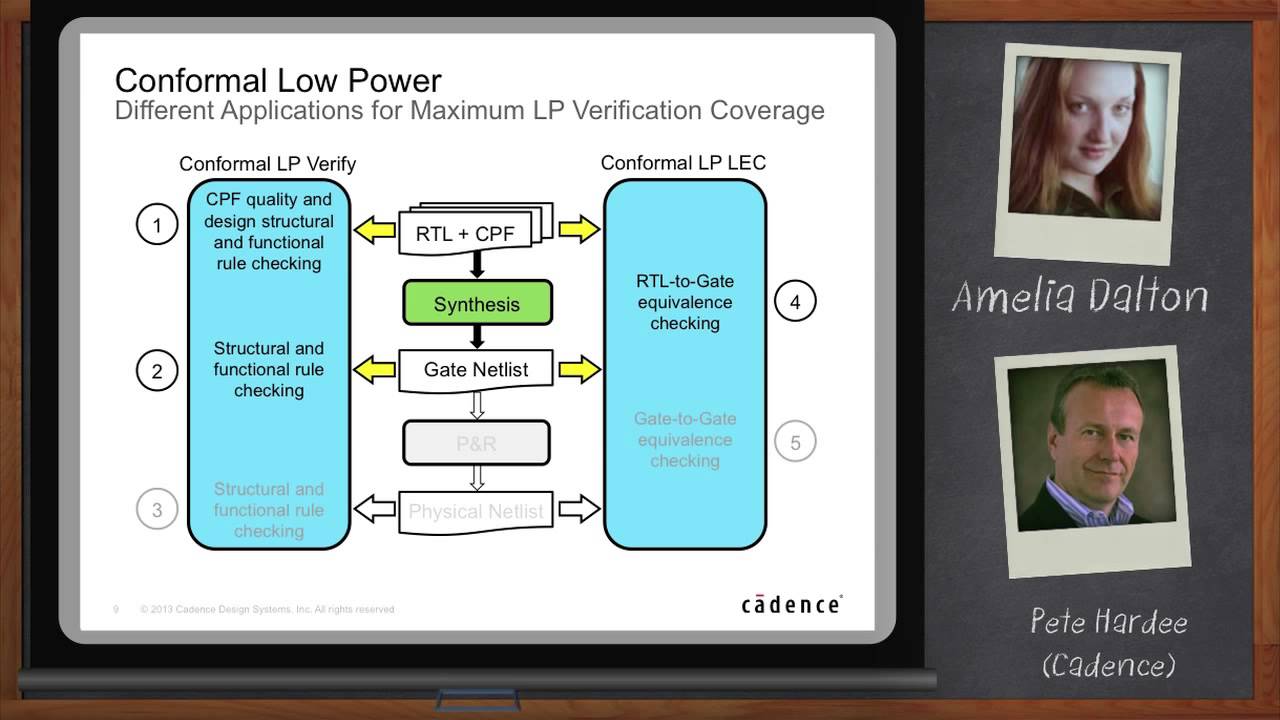

Cadence Low Power Solution RTL to GDSII Low Power Design — Cadence

Cadence Low Power Solution RTL to GDSII Low Power Design — Cadence

Related image with low power design techniques span rtl to gdsii flow ee times

Related image with low power design techniques span rtl to gdsii flow ee times

About "Low Power Design Techniques Span Rtl To Gdsii Flow Ee Times"

Comments are closed.