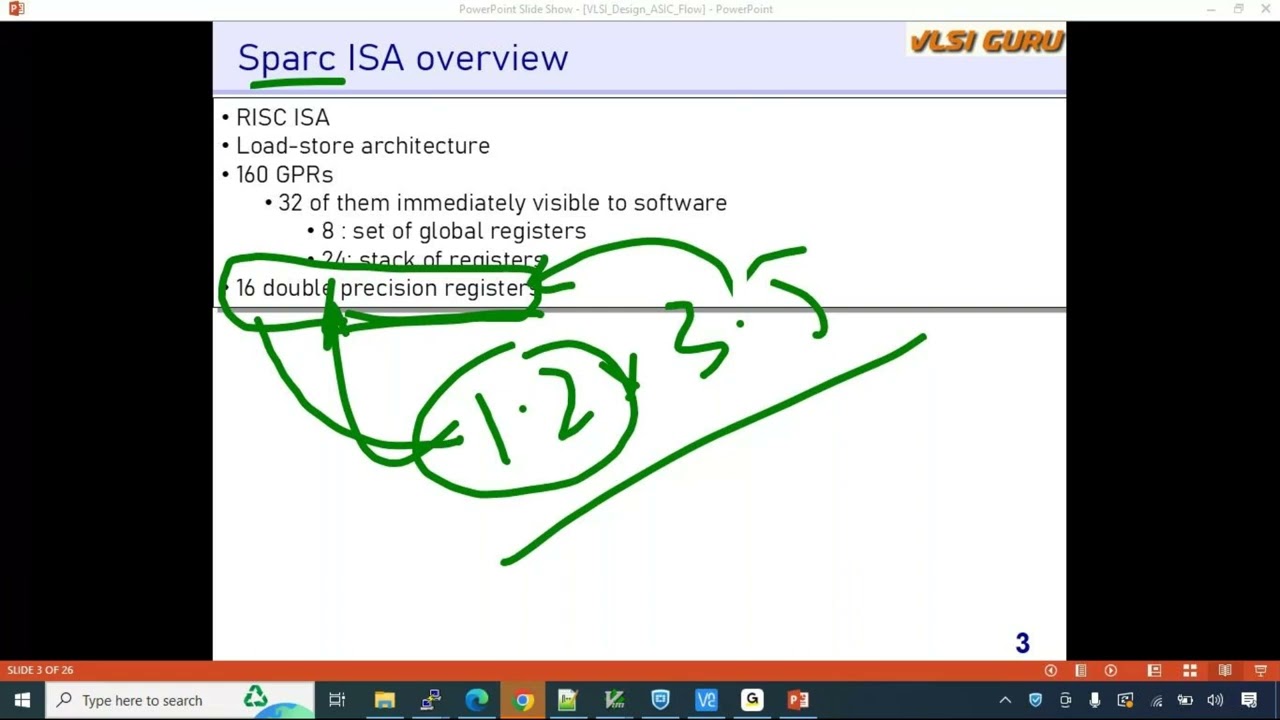

Sparc64bit Soc Rtl To Gdsii Flow Demo Session

Implementation Of RISC-V SoC From RTL To GDS Flow Using Open-Source Tools | PDF | Logic ...

Implementation Of RISC-V SoC From RTL To GDS Flow Using Open-Source Tools | PDF | Logic ... This series of videos will demonstrate the full flow from rtl to gdsii with live eda tools session.this series of videos will demonstrate the full flow from rtl to gdsii with live eda. In this guide, we’ll break down the rtl to gdsii process step by step, explain where outsourcing adds value, and how nsemi design ensures quality across the entire flow. what is rtl to gdsii?.

Complete RTL To GDSII Flow For “Analog On Top” Designs | Siemens Software

Complete RTL To GDSII Flow For “Analog On Top” Designs | Siemens Software This tutorial teaches how to implement a design idea from rtl to gdsii flow using cadence® tools. you will learn how to deal with these challenges while running the flow, such as resolving errors in the log file, debugging the timing violations, and fixing setup and hold violations. Reference flow 8.0 incorporates comprehensive synopsys based rtl to gdsii using the galaxy design platform for rtl synthesis, physical implementation and sign off, and the discovery™ verification platform with vcs®, hspice®, and hsim™/nanosim® for rtl verification and circuit simulation. In this cadence training webinar, we explore the concepts of rtl design, design verification, and coverage analysis while unveiling the exciting world of front end design flow. we will guide you through the essential steps in creating integrated circuits. Here i have demonstrated the process of converting a rtl to gds ii.this is a two weeks workshop organized by vsd in association with nasscom. this is an arduino microcontroller board. the encircled area shows the chip (microprocessor) which is interfaced with other components of the board.

Tool Flow Depicting RTL To GDSII Flow | Download Scientific Diagram

Tool Flow Depicting RTL To GDSII Flow | Download Scientific Diagram In this cadence training webinar, we explore the concepts of rtl design, design verification, and coverage analysis while unveiling the exciting world of front end design flow. we will guide you through the essential steps in creating integrated circuits. Here i have demonstrated the process of converting a rtl to gds ii.this is a two weeks workshop organized by vsd in association with nasscom. this is an arduino microcontroller board. the encircled area shows the chip (microprocessor) which is interfaced with other components of the board. This session is specially curated for vlsi enthusiasts, students, and professionals who want to understand the industry standard flow. 🔹 what you’ll learn in this demo: rtl to gdsii. In this recent training webinar, we explore the concepts of rtl design, design verification, and coverage analysis while unveiling the exciting world of front end design flow by guiding you through essential steps involved in creating integrated circuits—the building blocks of modern electronics. In the field of very large scale integration (vlsi) design, the journey from register transfer level (rtl) to gdsii is a critical and intricate process. this transformation is pivotal for. In this tutorial, you learn how to implement a design from rtl to gdsii using cadence® tools. you will start by coding a design in verilog. you will simulate the coded design, followed by design synthesis and optimization. you will then run equivalency checks at different stages of the flow.

GitHub - Abdelazeem201/Cadence-RTL-to-GDSII-Flow: In This Tutorial, You Learn How To Implement A ...

GitHub - Abdelazeem201/Cadence-RTL-to-GDSII-Flow: In This Tutorial, You Learn How To Implement A ... This session is specially curated for vlsi enthusiasts, students, and professionals who want to understand the industry standard flow. 🔹 what you’ll learn in this demo: rtl to gdsii. In this recent training webinar, we explore the concepts of rtl design, design verification, and coverage analysis while unveiling the exciting world of front end design flow by guiding you through essential steps involved in creating integrated circuits—the building blocks of modern electronics. In the field of very large scale integration (vlsi) design, the journey from register transfer level (rtl) to gdsii is a critical and intricate process. this transformation is pivotal for. In this tutorial, you learn how to implement a design from rtl to gdsii using cadence® tools. you will start by coding a design in verilog. you will simulate the coded design, followed by design synthesis and optimization. you will then run equivalency checks at different stages of the flow.

Sparc64bit SOC RTL to GDSII flow demo session

Sparc64bit SOC RTL to GDSII flow demo session

Related image with sparc64bit soc rtl to gdsii flow demo session

Related image with sparc64bit soc rtl to gdsii flow demo session

About "Sparc64bit Soc Rtl To Gdsii Flow Demo Session"

Comments are closed.